### **Digitally Enhanced Power Analog Synchronous Low-Side PWM Controller**

### Features:

- Input Voltage: 4.5V to 42V

- Can be configured with Multiple Topologies including but not limited to:

- Flyback

- Ćuk

- -B oost

- SEPIC (Single-Ended Primary-Inductor Converter)

- Capable of Quasi-Resonant or Fixed-Frequency

Operation

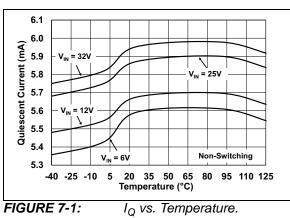

- · Low Quiescent Current: 5 mA Typical

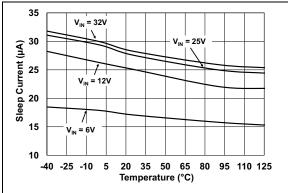

- Low Sleep Current: 30 µA Typical

- Low-Side Gate Drivers:

- +5V Gate Drive

- 0.5A Sink/Source Current

- -+ 10V Gate Drive

- 1A Sink/Source Current

- Peak Current Mode Control

- Differential Remote Output Sense

- Multiple Output Systems:

- Master or Slave

- Configurable Parameters:

- -V <sub>REF</sub>, Precision I<sub>OUT</sub>/V<sub>OUT</sub> Set Point (DAC)

- Input Undervoltage Lockout (UVLO)

- Input Overvoltage Lockout (OVLO)

- Detection and Protection

- Primary Current Leading Edge Blanking (0, 50 ns, 100 ns and 200 ns)

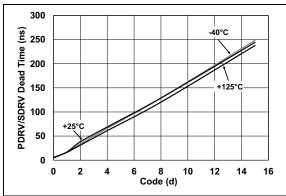

- Gate Drive Dead Time (16 ns to 256 ns)

- Fixed Switching Frequency Range: 31.25 kHz to 2.0 MHz

- Slope Compensation

- Quasi-Resonant Configuration with Built-in Comparator and Programmable Offset Voltage Adjustment

- Primary Current Offset Adjustment

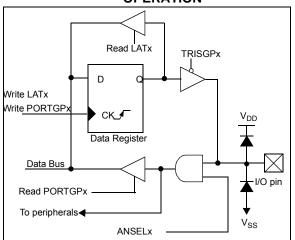

- Configurable GPIO Pin Options

- Integrated Low-Side Differential Current Sense

Amplifier

- ±5% Current Regulation

- · Thermal Shutdown

### **Microcontroller Features:**

- Precision 8 MHz Internal Oscillator Block:

Sectors and instant of the 140% the missel

- Factory-calibrated to ±1%, typical

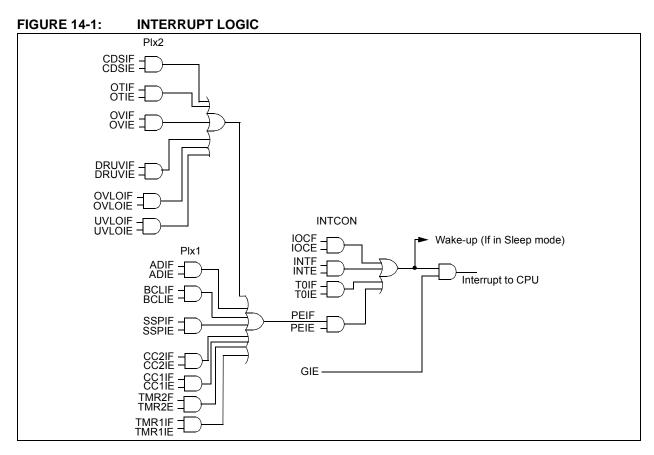

- Interrupt Capable

- -F irmware

- Interrupt-on-Change Pins

- Only 35 Instructions to Learn

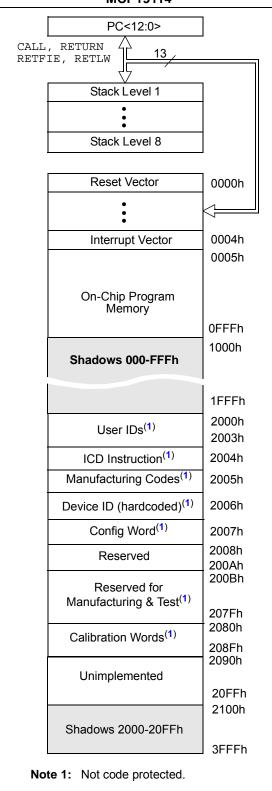

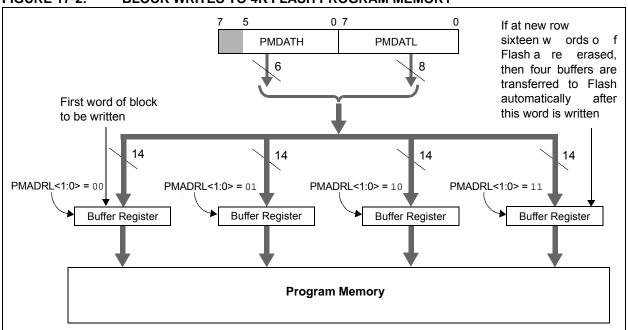

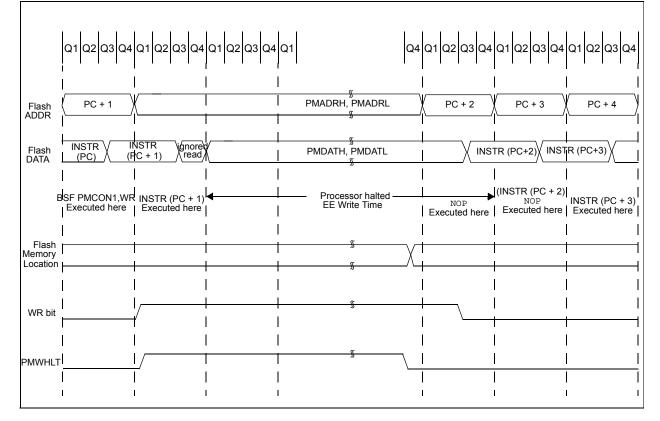

- 4096 Words On-Chip Program Memory

- High Endurance Flash:

- 100,000 write Flash Endurance

- Flash Retention: >40 years

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Programmable Code Protection

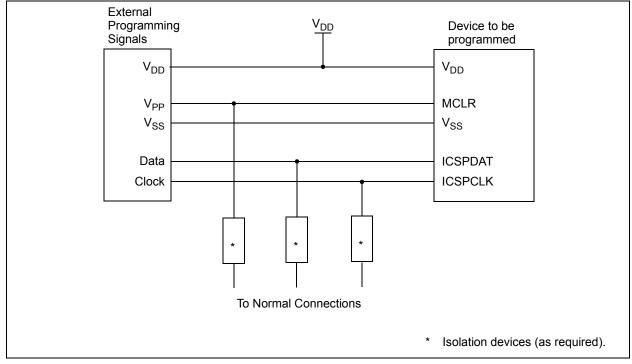

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- Eight I/O Pins and One Input-Only Pin

- Two Open Drain Pins

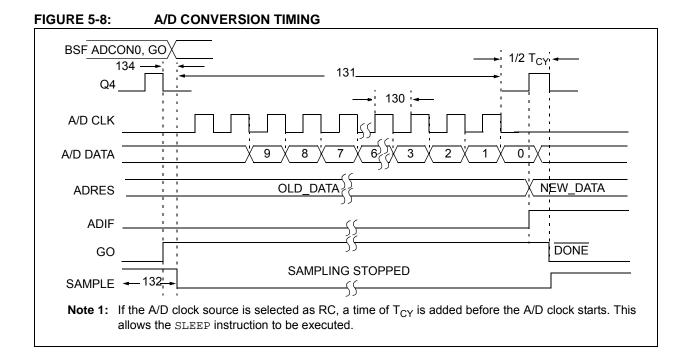

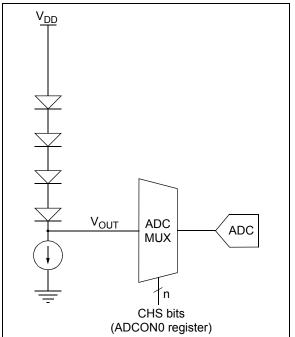

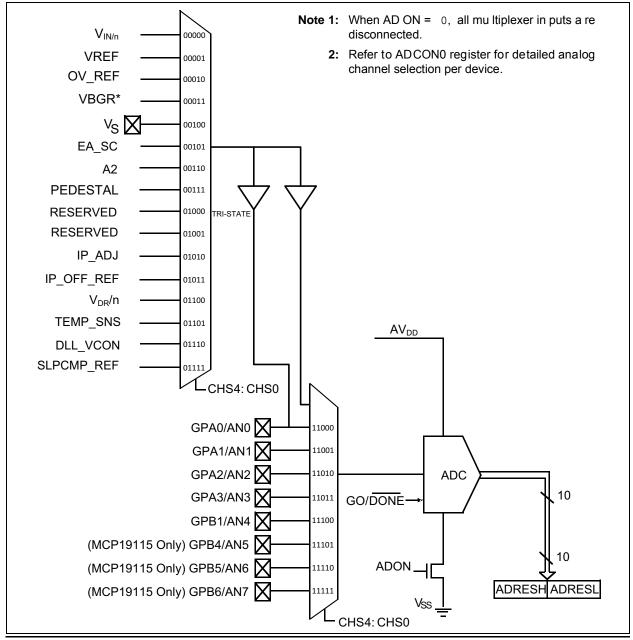

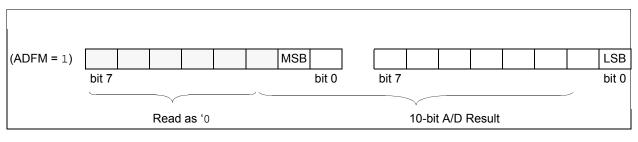

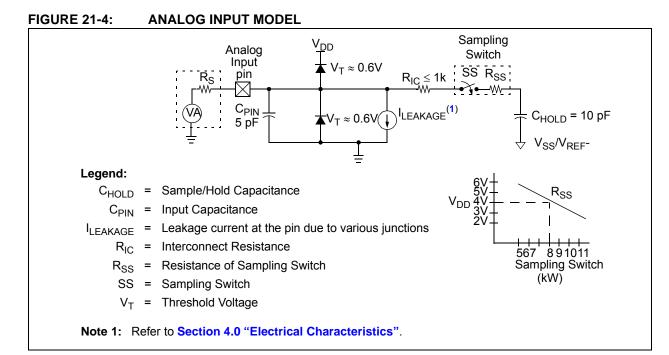

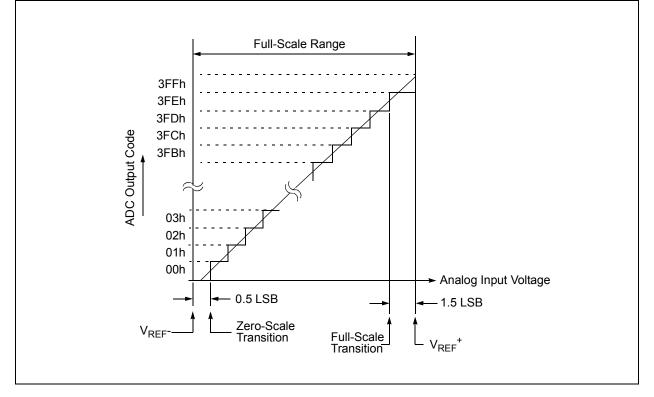

- Analog-to-Digital Converter (ADC):

- 10-bit Resolution

- Five External Channels

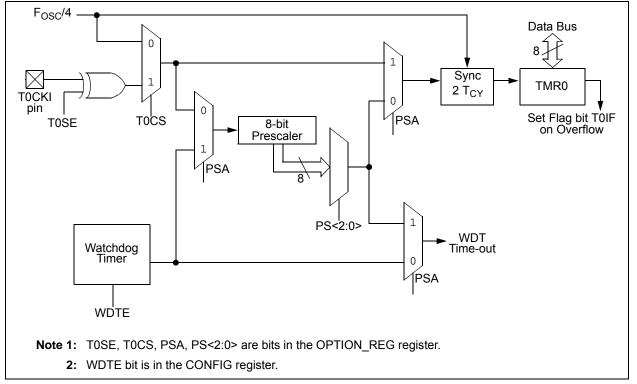

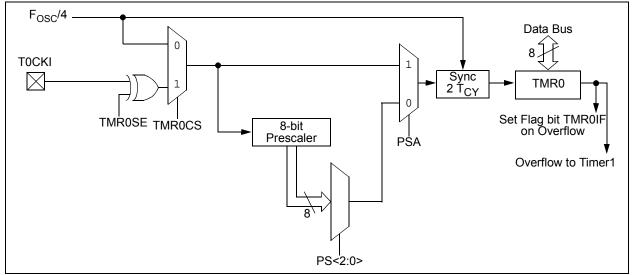

- Timer0: 8-bit Timer/Counter with 8-bit Prescaler

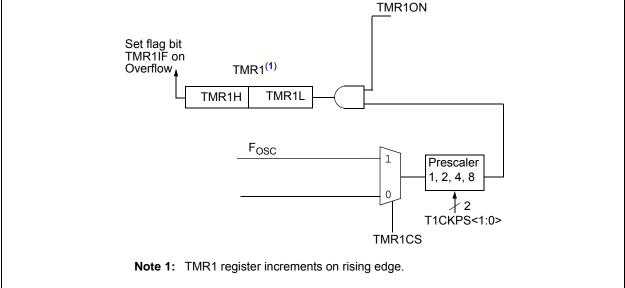

- Enhanced Timer1:

- 16-bit Timer with Prescaler

- Two Selectable Clock Sources

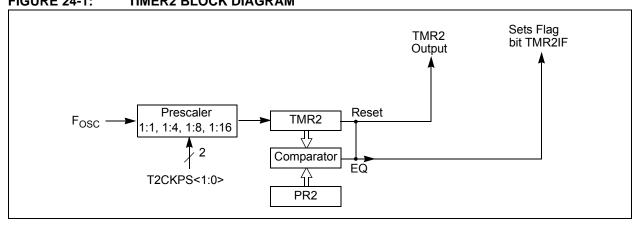

- Timer2: 8-Bit Timer with Prescaler

- 8-bit Period Register

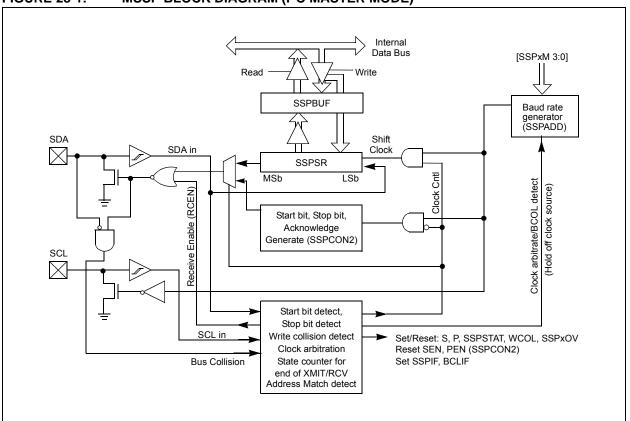

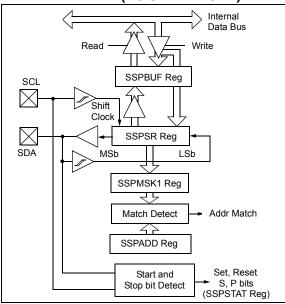

- I <sup>2</sup>C<sup>™</sup> Communication:

- 7-bit Address Masking

- Two Dedicated Address Registers

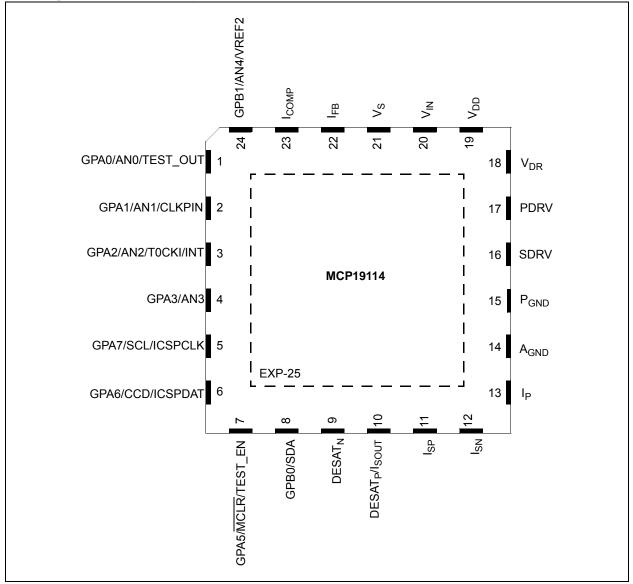

### Pin Diagram – 24-Pin QFN (MCP19114)

TABLE 1: 24-PIN SUMMARY

| TADLE I.                                  |            |       |     |        |      |                    |                  |                  |                                                                        |  |

|-------------------------------------------|------------|-------|-----|--------|------|--------------------|------------------|------------------|------------------------------------------------------------------------|--|

| Q                                         | 24-Pin QFN | ANSEL | A/D | Timers | MSSP | Interrupt          | Pull-up          | Basic            | Additional                                                             |  |

| GPA0                                      | 1          | Y     | AN0 | —      |      | IOC                | Y                | —                | Analog/Digital Debug Output <sup>(1)</sup>                             |  |

| GPA1                                      | 2          | Y     | AN1 | _      | _    | IOC                | Y                | —                | Sync Signal In/Out <sup>(2)</sup>                                      |  |

| GPA2                                      | 3          | Y     | AN2 | T0CKI  | _    | IOC<br>INT         | Y                | —                | _                                                                      |  |

| GPA3                                      | 4          | Y     | AN3 | _      | _    | IOC                | Y                | —                | —                                                                      |  |

| GPA5                                      | 7          | Ν     | _   | _      | _    | IOC <sup>(4)</sup> | Y <sup>(5)</sup> | MCLR             | Test Enable Input                                                      |  |

| GPA6                                      | 6          | Ν     | _   | —      |      | IOC                | Y                | ICSPDAT          | Dual Capture/Compare Input                                             |  |

| GPA7                                      | 5          | Ν     | _   | _      | SCL  | IOC                | Ν                | ICSPCLK          | —                                                                      |  |

| GPB0                                      | 8          | Ν     | _   | _      | SDA  | IOC                | Ν                | —                | —                                                                      |  |

| GPB1                                      | 24         | Y     | AN4 | —      | _    | IOC                | Y                | —                | V <sub>REF2</sub> <sup>(3)</sup>                                       |  |

| DESAT <sub>N</sub>                        | 9          | Ν     | _   | _      | _    | —                  | _                | —                | DESAT Negative Input                                                   |  |

| DESAT <sub>P</sub> /<br>I <sub>SOUT</sub> | 10         | Ν     | —   |        | —    | _                  | _                | —                | DESAT <sub>P</sub> Input or I <sub>SOUT</sub><br>Output <sup>(6)</sup> |  |

| I <sub>SP</sub>                           | 11         | Ν     | —   | —      | _    | —                  | Y                | —                | Current Sense Amplifier Positive<br>Input                              |  |

| I <sub>SN</sub>                           | 12         | Ν     | _   | —      | _    | —                  | _                | —                | Current Sense Amplifier<br>Negative Input                              |  |

| I <sub>P</sub>                            | 13         | Ν     | —   | —      | _    | —                  | _                | —                | Primary Input Current Sense                                            |  |

| A <sub>GND</sub>                          | 14         | Ν     | —   | —      | _    | —                  | _                | A <sub>GND</sub> | Small Signal Ground                                                    |  |

| P <sub>GND</sub>                          | 15         | Ν     | —   | —      |      | —                  | —                | P <sub>GND</sub> | Large Signal Ground                                                    |  |

| SDRV                                      | 16         | Ν     | —   |        | _    | _                  | _                | —                | Secondary LS Gate Drive<br>Output                                      |  |

| PDRV                                      | 17         | Ν     | —   | —      | _    | —                  |                  | —                | Primary LS Gate Drive<br>Output                                        |  |

| V <sub>DR</sub>                           | 18         | Ν     | —   | —      |      | —                  | _                | V <sub>DR</sub>  | Gate Drive Supply Voltage                                              |  |

| V <sub>DD</sub>                           | 19         | Ν     | _   | _      | _    | _                  | _                | V <sub>DD</sub>  | V <sub>DD</sub> Output                                                 |  |

| V <sub>IN</sub>                           | 20         | Ν     | —   | —      |      | —                  | _                | V <sub>IN</sub>  | Input Supply Voltage                                                   |  |

| V <sub>S</sub>                            | 21         | Ν     |     | —      |      |                    |                  |                  | Output Voltage Sense                                                   |  |

| I <sub>FB</sub>                           | 22         | Ν     |     | _      |      | —                  |                  | —                | Error Amplifier Feedback Input                                         |  |

| I <sub>COMP</sub>                         | 23         | Ν     | —   | —      | _    | —                  | _                | —                | Error Amplifier Output                                                 |  |

| Nata 4.                                   |            |       |     |        |      |                    |                  |                  |                                                                        |  |

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

- 2: Selected w hen functioning as master or s lave by proper configuration of the MSC <1:0> bits in the MODECON register.

- 3: V<sub>REF2</sub> output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

- **4:** The IOC is disabled when  $\overline{\text{MCLR}}$  is enabled.

- 5: Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

- 6: When RFB of MODECON<5> = 0, internal feedback resistor and DESAT<sub>P</sub> input are enabled. When RFB = 1,  $I_{SOUT}$  is enabled.

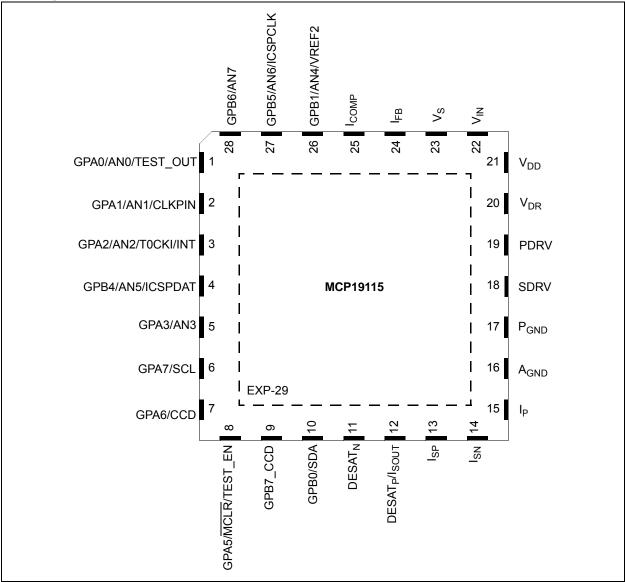

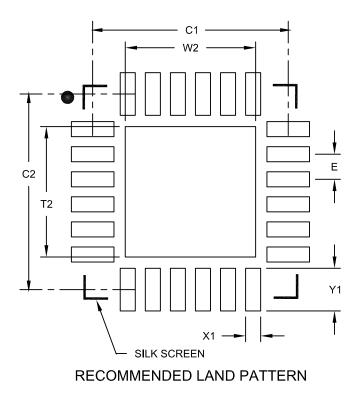

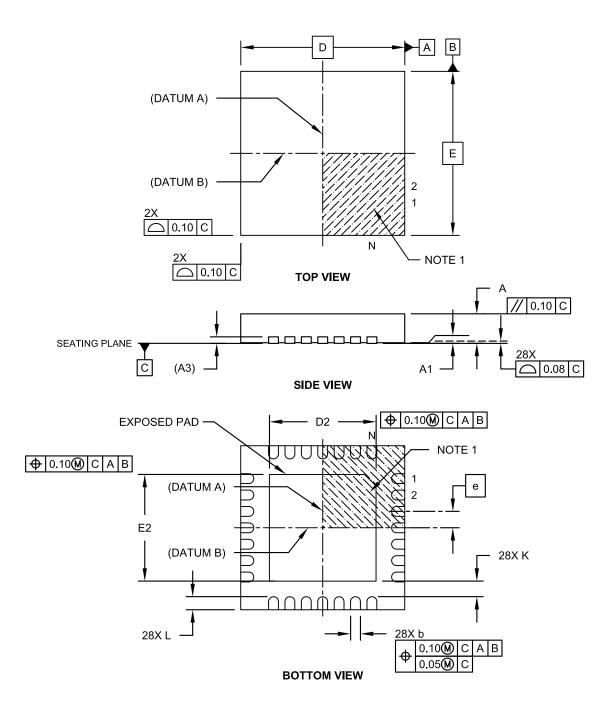

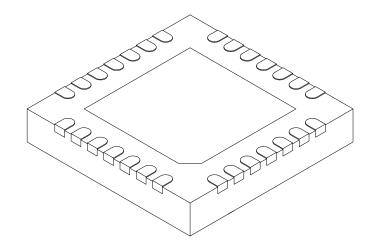

### Pin Diagram – 28-Pin QFN (MCP19115)

TABLE 2: 28-PIN SUMMARY

| TADLE Z.                                  | 20-FIN SUMIWART |       |     |        |      |                    |                  |                  |                                                                        |  |

|-------------------------------------------|-----------------|-------|-----|--------|------|--------------------|------------------|------------------|------------------------------------------------------------------------|--|

| 0/1                                       | 28-Pin QFN      | ANSEL | A/D | Timers | MSSP | Interrupt          | Pull-up          | Basic            | Additional                                                             |  |

| GPA0                                      | 1               | Y     | AN0 | —      | _    | IOC                | Y                | —                | Analog/Digital Debug Output <sup>(1)</sup>                             |  |

| GPA1                                      | 2               | Y     | AN1 | _      |      | IOC                | Y                | _                | Sync Signal In/Out <sup>(2)</sup>                                      |  |

| GPA2                                      | 3               | Y     | AN2 | TOCKI  | —    | IOC<br>INT         | Y                |                  | _                                                                      |  |

| GPA3                                      | 5               | Y     | AN3 | _      |      | IOC                | Y                | _                | _                                                                      |  |

| GPA5                                      | 8               | Ν     |     |        |      | IOC <sup>(4)</sup> | Y <sup>(5)</sup> | MCLR             | Test Enable Input                                                      |  |

| GPA6                                      | 7               | N     | _   | —      | —    | IOC                | Y                | _                | Dual Capture/Single<br>Compare1 Input                                  |  |

| GPA7                                      | 6               | Ν     | _   | —      | SCL  | IOC                | Ν                | —                | —                                                                      |  |

| GPB0                                      | 10              | Ν     | —   | —      | SDA  | IOC                | Ν                | —                | —                                                                      |  |

| GPB1                                      | 26              | Y     | AN4 | —      | _    | IOC                | Y                | —                | V <sub>REF2</sub> <sup>(3)</sup>                                       |  |

| GPB4                                      | 4               | Y     | AN5 | —      | _    | IOC                | Y                | ICSPDAT          | —                                                                      |  |

| GPB5                                      | 27              | Y     | AN6 | —      | _    | IOC                | Y                | ICSPCLK          | —                                                                      |  |

| GPB6                                      | 28              | Y     | AN7 | —      | _    | IOC                | Y                | —                | —                                                                      |  |

| GPB7                                      | 9               | Y     | _   | —      | _    | IOC                | Y                | —                | Single Compare2 Input                                                  |  |

| DESAT <sub>P</sub> /<br>I <sub>SOUT</sub> | 12              | N     | —   | —      | _    | —                  | _                | —                | DESAT <sub>P</sub> input or I <sub>SOUT</sub><br>Output <sup>(6)</sup> |  |

| DESAT <sub>N</sub>                        | 11              | Ν     |     | —      | _    | _                  |                  |                  | DESAT Negative Input                                                   |  |

| I <sub>SP</sub>                           | 13              | N     | —   | —      | _    | —                  | Y                | —                | Current Sense Amplifier<br>Non-Inverting Input                         |  |

| I <sub>SN</sub>                           | 14              | N     | —   | —      | —    | —                  |                  | —                | Current Sense Amplifier<br>Inverting Input                             |  |

| l <sub>P</sub>                            | 15              | Ν     | _   | —      | _    | —                  | _                |                  | Primary Input Current Sense                                            |  |

| A <sub>GND</sub>                          | 16              | Ν     |     | —      | _    | _                  |                  | A <sub>GND</sub> | Small Signal Ground                                                    |  |

| P <sub>GND</sub>                          | 17              | Ν     | _   | —      | _    | —                  | _                | P <sub>GND</sub> | Large Signal Ground                                                    |  |

| SDRV                                      | 18              | N     | —   | —      | —    | —                  | _                | —                | Secondary LS Gate Drive<br>Output                                      |  |

| PDRV                                      | 19              | Ν     | —   | —      | _    | —                  | _                | —                | Primary LS Gate Drive Output                                           |  |

| V <sub>DR</sub>                           | 20              | Ν     | —   | —      | _    | —                  | _                | V <sub>DR</sub>  | Gate Drive Supply Voltage                                              |  |

| V <sub>DD</sub>                           | 21              | Ν     | —   | —      |      | —                  |                  | V <sub>DD</sub>  | V <sub>DD</sub> Output                                                 |  |

| V <sub>IN</sub>                           | 22              | Ν     | —   | —      | _    | —                  | _                | V <sub>IN</sub>  | Input Supply Voltage                                                   |  |

| V <sub>S</sub>                            | 23              | Ν     | —   | —      | _    | —                  | _                | —                | Output Voltage Sense                                                   |  |

| I <sub>FB</sub>                           | 24              | Ν     | —   | —      | _    | —                  | _                | —                | Error Amplifier Feedback input                                         |  |

| I <sub>COMP</sub>                         | 25              | Ν     |     | —      |      | —                  |                  |                  | Error Amplifier Output                                                 |  |

|                                           |                 |       |     |        |      | otod thro          | ugh tha a        | ontrol of the A  | RECON register                                                         |  |

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

2: Selected w hen functioning as master or s lave by p roper c onfiguration of the M SC<1:0> b its in t he MODECON register.

- **3:** VREF2 output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

- **4:** The IOC is disabled when  $\overline{\text{MCLR}}$  is enabled.

- 5: Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

- 6: When RFB of MODECON<6> =0 Internal feedback resistor is enabled allow with DESAT<sub>P</sub> input. When RFB=1, I<sub>SOUT</sub> is enabled.

### **Table of Contents**

| 1.0   | Device Overview                              |     |

|-------|----------------------------------------------|-----|

| 2.0   | Pin Description                              | 13  |

| 3.0   | Functional Description                       | 19  |

| 4.0   | Electrical Characteristics                   |     |

| 5.0   | Digital Electrical Characteristics           | 29  |

| 6.0   | Configuring the MCP19114/5                   | 37  |

| 7.0   | Typical Performance Curves                   |     |

| 8.0   | System Bench Testing                         | 57  |

| 9.0   | Device Calibration                           | 59  |

| 10.0  | Memory Organization                          | 67  |

| 11.0  | Device Configuration                         | 79  |

| 12.0  | Oscillator Modes                             | 81  |

| 13.0  | Resets                                       |     |

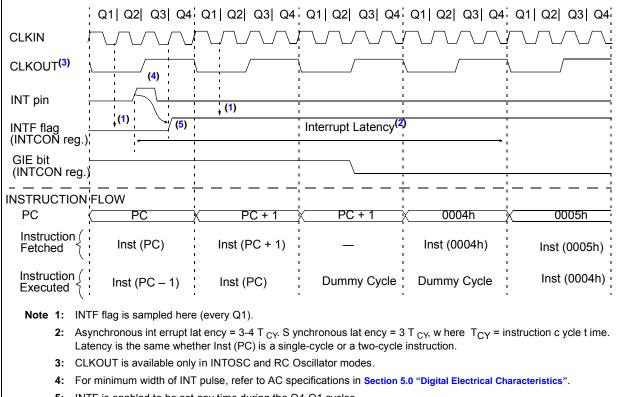

| 14.0  | Interrupts                                   |     |

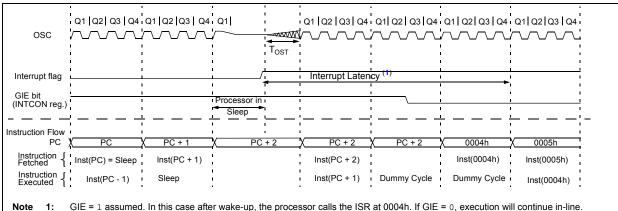

| 15.0  | Power-Down Mode (Sleep)                      | 99  |

| 16.0  | Watchdog Timer (WDT)                         | 101 |

| 17.0  | Flash Program Memory Control                 | 103 |

| 18.0  | I/O Ports                                    | 109 |

| 19.0  | Interrupt-On-Change                          | 119 |

| 20.0  | Internal Temperature Indicator Module        | 123 |

| 21.0  | Analog-to-Digital Converter (ADC) Module     | 125 |

|       | Timer0 Module                                |     |

| 23.0  | Timer1 Module with Gate Control              | 137 |

| 24.0  | Timer2 Module                                | 141 |

| 25.0  | Enhanced PWM Module                          |     |

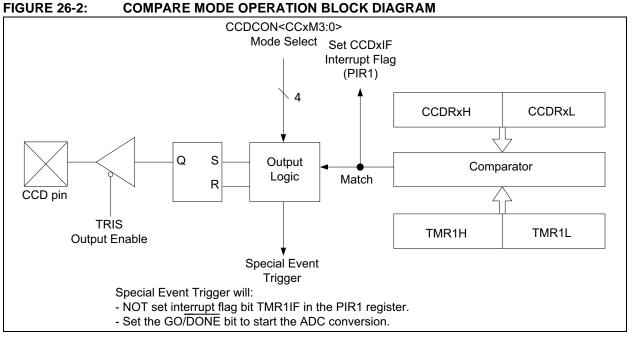

| 26.0  | Dual Capture/Compare (CCD) Module            | 147 |

| 27.0  | PWM Control Logic                            |     |

| 28.0  | Master Synchronous Serial Port (MSSP) Module | 153 |

| 29.0  | Instruction Set Summary                      | 195 |

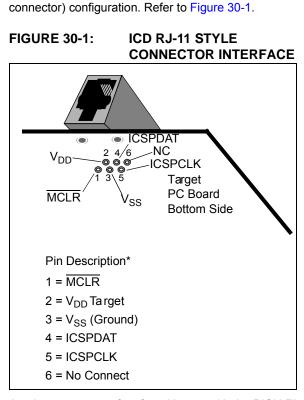

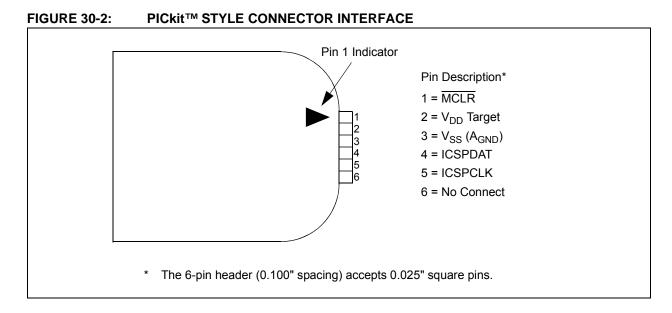

| 30.0  | In-Circuit Serial Programming™ (ICSP™)       |     |

| 31.0  | Development Support                          | 207 |

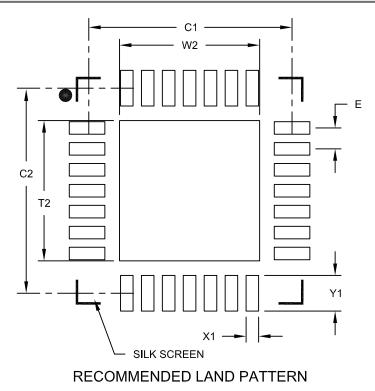

| 32.0  | Packaging Information                        | 211 |

| Appe  | ndix A: Revision History                     | 217 |

| Index | ·                                            | 219 |

| The N | /icrochip Web Site                           | 225 |

| Custo | omer Change Notification Service             | 225 |

| Custo | omer Support                                 | 225 |

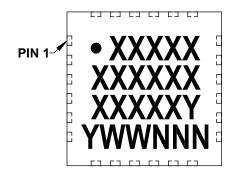

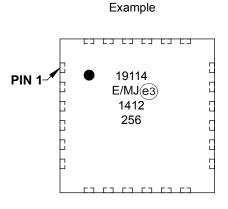

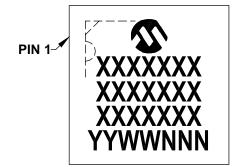

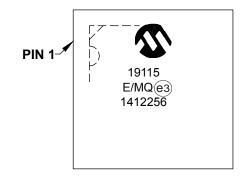

| Produ | uct Identification System                    | 227 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

### 1.0 DEVICE OVERVIEW

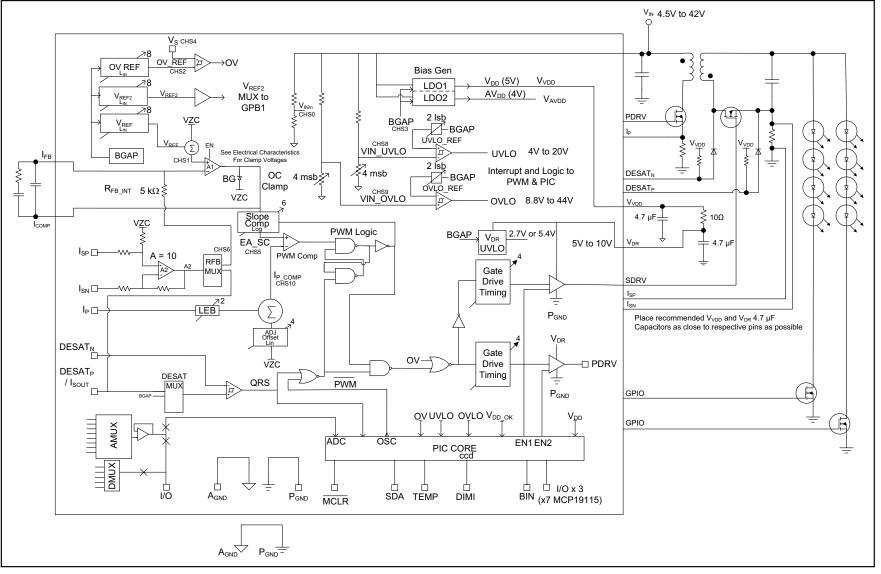

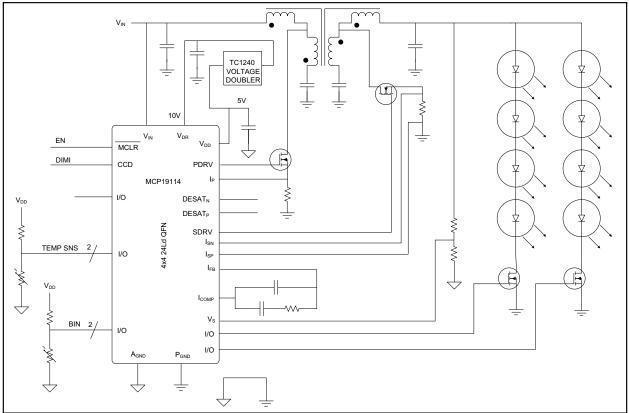

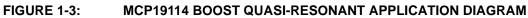

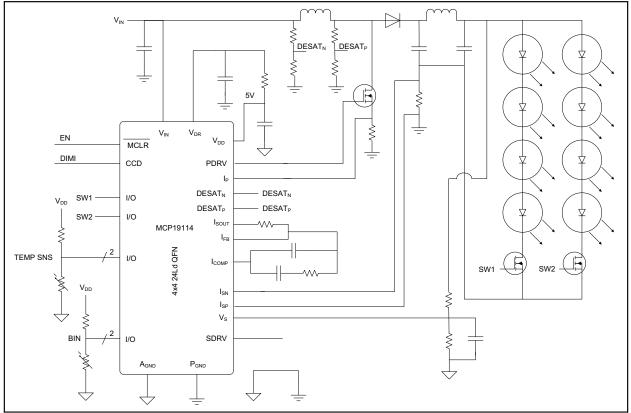

The MCP19114/5 are h ighly integrated, mixed signal low-side s ynchronous c ontrollers that o perate from 4.5V t o 4 2V. T he f amily fe atures an an alog PW M controller with an integrated microcontroller core used for LED lighting systems, battery chargers and other low-side switch PWM applications. The devices feature an ana log int ernal PWM controller similar to th e MCP1631, and a standard PIC<sup>®</sup> microcontroller similar to the PIC12F617.

Complete c ustomization of d evice o perating parameters, s tart-up or s hutdown profiles, protection levels and fault handling procedures are accomplished by setting digital registers using Microchip's MPLAB<sup>®</sup> X Integrated D evelopment Environment s oftware a nd one of Microchip's many in-circuit debugger and device programmers.

The MCP19114/5 mixed signal low-side synchronous controllers fe ature in tegrated pr ogrammable input UVLO/OVLO, programmable output overvoltage (OV), two lo w-side g ate dri ve out puts w ith i ndependent programmable dead time, programmable leading edge blanking (fo ur st eps), pro grammable 6-b it s lope compensation and an inte grated int ernal programmable oscillator f or fi xed-frequency applications. An int egrated 8-bit reference vol tage (V<sub>REF</sub>) is used for setting output voltage or current. An internal co mparator s upports quasi-resonant applications. Add itional C apture a nd C ompare modules are integrated for additional control, including enhanced di mming ca pability. Th e MC P19114/5 devices contain two internal LDOs. A 5V LDO is used to pow er the i nternal proc essor and provide 5V externally. T his 5V e xternal ou tput ca n b e us ed to supply the gate drive. An analog filter between the V<sub>DD</sub> output and the V DR input is re commended when implementing a 5V gate drive supplied from V<sub>DD</sub>. Two 4.7 µF capacitors are recommended with one placed as c lose a s po ssible to  $\,$  V  $_{DD}$  a nd o ne a s c lose a s possible to  $V_{DR},$  separated by a  $10\Omega$  isolation resistor. DO NOT exceed 10 µF on the V<sub>DD</sub>. An external supply is required to implement higher gate drive voltages. By utilizing Microchip's TC1240A voltage doubler supplied from V  $_{DD}$  to provide V  $_{DR}$ , a 10 V gate drive can be achieved. A 4V LD O is us ed t o po wer the int ernal analog circuitry. The two low-side drivers can be used to operate the power converter in bidirectional mode, enabling the "shaping" of LED dimming current in LED applications or de veloping bid irectional po wer converters for battery-powered applications.

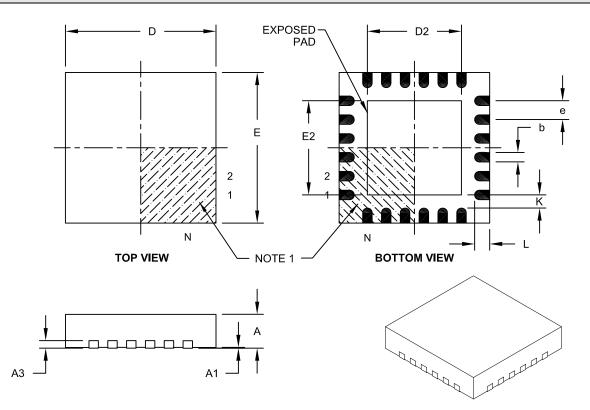

The MCP19114 is packaged in a 24-lead 4 mm x 4 mm QFN. T he MCP19115 i s packaged i n a 2 8-lead 5 mm x 5 mm QFN.

The ab ility for sy stem designers t o configure application-specific features allows the MCP19114/5 to be offered in smaller packages than currently available in in tegrated de vices tod ay. T he G eneral Purp ose Input/Output (G PIO) of th e MC P19114/5 c an b e configured to offer a status output, a device enable, to control a n ex ternal sw itch, a s witching fre quency synchronization output or input or even a device status or "h eartbeat" indicator. T his f lexibility allows th e MCP19114/5 packages and complete solutions to be smaller, thereby sa ving si ze and cost of t he sy stem printed circuit boards.

With integrated features like output current adjust and dynamic output voltage positioning, the MCP19114/5 family has the best in class performance and highest integration level currently available.

Power trains supported by this architecture include but are not limited to bo ost, fly back, quasi-resonant flyback, SEPIC, Ćuk, etc. Two low-side gate drivers are capable of sinking and sourcing 1A at 10V  $V_{DR}$ . With a 5V gate drive, the driver is capable of 0.5A sink and source. The user has the option to allow the VIN UVLO to shut down the drivers by setting the UVLOEN bit. When this bit is not set, the device drivers will ride through the UVLO condition and continue to operate until V DR reaches the gate drive U VLO v alue. This value is s electable at 2.7V or 5.4V and is al ways enabled. An internal reset for the microcontroller core is set to 2.0V. An internal comparator module is used to sense the desaturation of the fly back trans former to synchronize switching for quasi-resonant applications. The operating input voltage for normal device operation ranges from 4.5V to 42V with an absolute maximum of 44V. The maximum transient voltage is 48V for 500 ms. An I<sup>2</sup>C serial bus is used for d evice communications from the PWM controller to the system.

### MCP19114/5 FLYBACK SYNCHRONOUS QUASI-RESONANT BLOCK DIAGRAM

**MCP19114/5**

### 2.0 PIN DESCRIPTION

The 24-lead M CP19114 a nd 28-lead M CP19115 devices fe ature pi ns that have m ultiple functions associated with each pi n. Table 2-1 provides a description of the different functions. Refer to **Section 2.1 "Detailed Pin Functional Description"** for more detailed information.

| Name               | Function | Input<br>Type     | Output<br>Type | Description                                                      |  |  |  |  |

|--------------------|----------|-------------------|----------------|------------------------------------------------------------------|--|--|--|--|

| GPA0/AN0/TEST_OUT  | GPA0     | TTL               | CMOS           | General-purpose I/O                                              |  |  |  |  |

|                    | AN0      | AN                | _              | A/D Channel 0 input                                              |  |  |  |  |

|                    | TEST_OUT | _                 | _              | Internal analog/digital signal multiplexer output <sup>(1)</sup> |  |  |  |  |

| GPA1/AN1/CLKPIN    | GPA1     | TTL               | CMOS           | General-purpose I/O                                              |  |  |  |  |

|                    | AN1      | AN                | _              | A/D Channel 1 input                                              |  |  |  |  |

|                    | CLKPIN   | ST                | CMOS           | Switching frequency clock input or output <sup>(2)</sup>         |  |  |  |  |

| GPA2/AN2/T0CKI/INT | GPA2     | ST                | CMOS           | General-purpose I/O                                              |  |  |  |  |

|                    | AN2      | AN                | _              | A/D Channel 2 input                                              |  |  |  |  |

|                    | TOCKI    | ST                | _              | Timer0 clock input                                               |  |  |  |  |

|                    | INT      | ST                | _              | External interrupt                                               |  |  |  |  |

| GPA3/AN3           | GPA3     | TTL               | CMOS           | General-purpose I/O                                              |  |  |  |  |

|                    | AN3      | AN                | _              | A/D Channel 3 input                                              |  |  |  |  |

| GPA5/MCLR          | GPA5     | TTL               | —              | General-purpose input only                                       |  |  |  |  |

|                    | MCLR     | ST                | _              | Master Clear with internal pull-up                               |  |  |  |  |

| GPA6/CCD/ICSPDAT   | GPA6     | ST                | CMOS           | General-purpose I/O                                              |  |  |  |  |

|                    | ICSPDAT  | ST                | CMOS           | Serial Programming Data I/O                                      |  |  |  |  |

|                    | CCD      | ST                | CMOS           | Single Compare output. Dual Capture input                        |  |  |  |  |

| GPA7/SCL/ICSPCLK   | GPA7     | ST                | OD             | General-purpose open drain I/O                                   |  |  |  |  |

|                    | SCL      | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C clock                                           |  |  |  |  |

|                    | ICSPCLK  | ST                | _              | Serial Programming Clock                                         |  |  |  |  |

| GPB0/SDA           | GPB0     | TTL               | OD             | General-purpose I/O                                              |  |  |  |  |

|                    | SDA      | l <sup>2</sup> C™ | OD             | I <sup>2</sup> C data input/output                               |  |  |  |  |

| GPB1/AN4/VREF2     | GPB1     | TTL               | CMOS           | General-purpose I/O                                              |  |  |  |  |

|                    | AN4      | AN                | —              | A/D Channel 4 input                                              |  |  |  |  |

|                    | VREF2    | —                 | AN             | VREF2 DAC Output <sup>(3)</sup>                                  |  |  |  |  |

| GPB4/AN5/ICSPDAT   | GPB4     | TTL               | CMOS           | General-purpose I/O                                              |  |  |  |  |

| (MCP19115 Only)    | AN5      | AN                | _              | A/D Channel 5 input                                              |  |  |  |  |

|                    | ICSPDAT  | ST                | CMOS           | Primary Serial Programming Data I/O                              |  |  |  |  |

| GPB5/AN6/ICSPCLK   | GPB5     | TTL               | CMOS           | General-purpose I/O                                              |  |  |  |  |

| (MCP19115 Only)    | AN6      | AN                |                | A/D Channel 6 input                                              |  |  |  |  |

|                    | ISCPCLK  | ST                |                | Primary Serial Programming Clock                                 |  |  |  |  |

TABLE 2-1: MCP19114/5 PINOUT DESCRIPTION

Legend:AN= Analog input or output CMOS= CMOS compatible input or outputOD = Open DrainTTL= TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C$ = Schmitt Trigger input with  $I^2C$

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON register.

2: Selected when functioning as master or slave by proper configuration of the MSC<1:0> bits in the MODECON register.

**3:** VREF2 output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

| Name                                  | Function                              | Input<br>Type | Output<br>Type | Description                                                                                                              |  |  |  |

|---------------------------------------|---------------------------------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPB6/AN7                              | GPB6                                  | TTL           | CMOS           | General-purpose I/O                                                                                                      |  |  |  |

| (MCP19115 Only)                       | AN7                                   | AN            | _              | A/D Channel 7 input                                                                                                      |  |  |  |

| GPB7/CCD                              | GPB7                                  | TTL           | CMOS           | General-purpose I/O                                                                                                      |  |  |  |

| ( <b>MCP19115</b> Only)               | CCD                                   | ST            | CMOS           | Single Compare output. Dual Capture input.                                                                               |  |  |  |

| V <sub>IN</sub>                       | V <sub>IN</sub>                       | —             |                | Device input supply voltage                                                                                              |  |  |  |

| V <sub>DD</sub>                       | V <sub>DD</sub>                       |               |                | Internal +5V LDO output pin                                                                                              |  |  |  |

| V <sub>DR</sub>                       | V <sub>DR</sub>                       | —             |                | Gate drive supply voltage                                                                                                |  |  |  |

| A <sub>GND</sub>                      | A <sub>GND</sub>                      |               |                | Small signal quiet ground                                                                                                |  |  |  |

| P <sub>GND</sub>                      | P <sub>GND</sub>                      |               |                | Large signal power ground                                                                                                |  |  |  |

| PDRV                                  | PDRV                                  |               | _              | Primary Low-Side MOSFET gate drive                                                                                       |  |  |  |

| SDRV                                  | SDRV                                  |               |                | Secondary Low-Side MOSFET gate drive                                                                                     |  |  |  |

| I <sub>P</sub>                        | l <sub>P</sub>                        |               |                | Primary input current sense                                                                                              |  |  |  |

| I <sub>SN</sub>                       | I <sub>SN</sub>                       |               | _              | Secondary current sense amplifier negative input                                                                         |  |  |  |

| I <sub>SP</sub>                       | I <sub>SP</sub>                       |               | _              | Secondary current sense amplifier positive input                                                                         |  |  |  |

| V <sub>S</sub>                        | Vs                                    |               |                | Sense voltage compared to overvoltage DAC                                                                                |  |  |  |

| I <sub>FB</sub>                       | I <sub>FB</sub>                       |               | _              | Error amplifier feedback input                                                                                           |  |  |  |

| I <sub>COMP</sub>                     | I <sub>COMP</sub>                     | —             | _              | Error amplifier output                                                                                                   |  |  |  |

| DESAT <sub>P</sub> /I <sub>SOUT</sub> | DESAT <sub>P</sub> /I <sub>SOUT</sub> | —             | —              | DESAT <sub>P</sub> : DESAT detect comparator positive input I <sub>SOUT</sub> : Secondary current sense amplifier output |  |  |  |

| DESAT <sub>N</sub>                    | DESAT <sub>N</sub>                    | —             | —              | DESAT <sub>N</sub> : DESAT detect comparator negative input                                                              |  |  |  |

Legend:AN= Analog input or output CMOS= CMOS compatible input or outputOD = Open DrainTTL= TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C$ = Schmitt Trigger input with I<sup>2</sup>C

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON register.

2: Selected when functioning as master or slave by proper configuration of the MSC<1:0> bits in the MODECON register.

**3:** VREF2 output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

### 2.1 Detailed Pin Functional Description

### 2.1.1 GPA0 PIN

GPA0 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN0 is an input to the A/D. To configure this pin to be read by the A/D on channel 0, bits TRISA0 and ANSA0 must be set.

The ABECON register can be configured to set this pin to the TEST\_OUT function. It is a buffered output of the internal an alog or digital signal multiplexers. An alog signals pre sent on this pin are controlled by th e ADCON0 register. Digital signals pre sent on this pin are controlled by the ABECON register.

### 2.1.2 GPA1 PIN

GPA1 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN1 is an input to the A/D. To configure this pin to be read by the A/D on channel 1, bits TRISA1 and ANSA1 must be set.

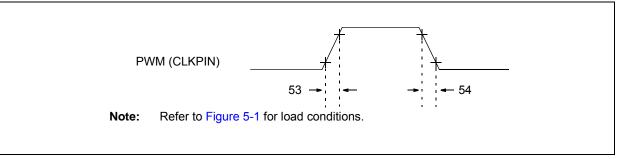

When the MCP19114/5 are configured as a MASTER or SLAVE, this pin is configured to be the switching frequency synchronization input or output (CLKPIN).

### 2.1.3 GPA2 PIN

GPA2 is a general-purpose ST input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN2 is an input to the A/D. To configure this pin to be read by the A/D on channel 2, bits TRISA2 and ANSA2 must be set.

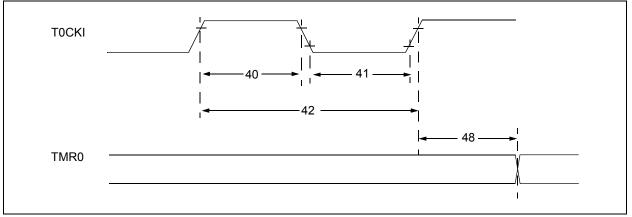

When bit T0CS is set in the OPTION\_REG register, the T0CKI function is enabled. Refer to Section 22.0 "Timer0 Module" for more information.

GPA2 can also be configured as an external interrupt by se tting the INTE bit . Refer to Section 14.2 "GPA2/INT Interrupt" for more information.

### 2.1.4 GPA3 PIN

GPA3 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN3 is an input to the A/D. To configure this pin to be read by the A/D on channel 3, bits TRISA3 and ANSA3 must be set.

### 2.1.5 GPA5 PIN

GPA5 is a g eneral-purpose TT L in put onl y p in. An internal weak pull-up and interrupt-on-change are also available.

For programming purposes, this pin is to be connected to the MCLR p in of the serial programmer. Refer to Section 30.0 "In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)" for more information.

This pin is MCLR when the MCLRE bit is set in the CONFIG register.

### 2.1.6 GPA6 PIN

GPA6 is a general-purpose CMOS output ST input pin whose data direction is controlled in TRISGPA.

ICSPDAT is a serial programming data I/O function. This can be used in conjunction with ICSPCLK to serial program the device.

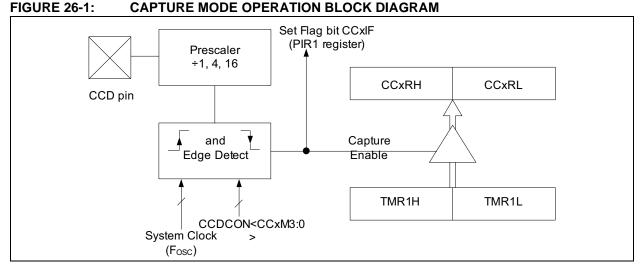

GPA6 is part of the CCD Module. For more information, refer to Section 26.0 "Dual Capture/Compare (CCD) Module".

### 2.1.7 GPA7 PIN

GPA7 is a true open drain general-purpose pin whose data direction is controlled in TR ISGPA. There is no internal connection between this pin and device  $V_{DD}$ . This pin d oes n ot have a w eak pull-up, b ut interrupt-on-change is available.

This pin is the primary ICSPCLK input. For MCP19115, this pin is AL T1\_ICSPCLK. This c an be used in conjunction with ICSPDAT to se rial program the device.

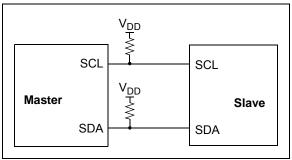

When the M CP19114/5 is configured for I  $^{2}$ C communication, Section 28.2 "I<sup>2</sup>C Mode Overview", GPA7 functions as the I<sup>2</sup>C clock (SCL). This pin must be configured as an input to allow proper operation.

### 2.1.8 GPB0 PIN

GPB0 is a true open drain general-purpose pin whose data direction is controlled in TRISGPB. There is no internal connection between this pin and device  $V_{DD}$ . This pin do es not hav e a w eak pull-up, but interrupt-on-change is available. Wh en th e MCP19114/5 are configured f or  $I^2C$  communication, **Section 28.2** " $I^2C$  **Mode Overview**", GPB0 functions as the  $I^2C$  clock (SDA). This pin must be configured as an input to allow proper operation.

### 2.1.9 GPB1 PIN

GPB1 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN4 is an input to the A/D. To configure this pin to be read by the A/D on channel 4, bits TRISB1 and ANSB1 must be set.

When the MCP19114/5 are configured as a MASTER, this pin is configured to be the  $V_{REF2}$  DAC output.

### 2.1.10 GPB4 PIN (MCP19115 ONLY)

GPB4 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN5 is an input to the A/D. To configure this pin to be read by the A/D on channel 5, bits TRISB4 and ANSB4 must be set.

ICSPDAT is the primary serial programming data I/O function. This is used in conjunction with ICSPCLK to serial program the device.

### 2.1.11 GPB5 PIN (MCP19115 ONLY)

GPB5 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN6 is an input to the A/D. To configure this pin to be read by the A/D on channel 6, bits TRISB5 and ANSB5 must be set.

ICSPCLK is the pri mary serial pro gramming cl ock function. This is used in conjunction with ICSPDAT to serial program the device.

### 2.1.12 GPB6 PIN (MCP19115 ONLY)

GPB6 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN7 is an input to the A/D. To configure this pin to be read by the A/D on channel 7, bits TRISB6 and ANSB6 must be set.

### 2.1.13 GPB7 PIN (MCP19115 ONLY)

GPB7 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

GPB7 is part of the CCD Module. For more information, refer to Section 26.0 "Dual Capture/Compare (CCD) Module".

### 2.1.14 DESAT<sub>N</sub> PIN

Internal comparator inverting input. U sed during quasi-resonant operation for desaturation detection.

### 2.1.15 DESAT<sub>P</sub>/I<sub>SOUT</sub> PIN

When using the internal comparator for d esaturation detection duri ng qu asi-resonant op eration, this pin connects to the comparator's non-inverting input. The output of the remote sense current sense amplifier gets configured to utilize the  $5 \text{ k}\Omega$  internal feedback resistor. When not ut ilizing the internal c omparator a nd no t configured to use the  $5 \text{ k}\Omega$  internal feedback resistor, the current sense amplifier gets connected to this pin and is I<sub>SOUT</sub>.

### 2.1.16 I<sub>SP</sub> PIN

The n on-inverting input t o i nternal cu rrent se nse amplifier, typically used to differentially remote sense secondary current. This pin can be internally pulled-up to  $V_{DD}$  by setting the <ISPUEN> bit in the PE1 register.

### 2.1.17 I<sub>SN</sub> PIN

The inverting input to internal current sense amplifier, typically used to differentially remote sense secondary current.

### 2.1.18 I<sub>P</sub> PIN

Primary input current sense for current mode control and peak current limit. For voltage mode control, this pin can be connected to an artificial ramp.

### 2.1.19 A<sub>GND</sub> PIN

$A_{GND}$  is the small signal ground connection pin. This pin should be connected to the exposed pad on the bottom of the package.

### 2.1.20 P<sub>GND</sub> PIN

Connect all large signal level ground returns to  $P_{GND}$ . These large-signal level ground traces should have a small loop area and minimal length to prevent coupling of switching noise to sensitive traces.

### 2.1.21 SDRV PIN

The ga te of the lo w-side s econdary MOSFET i s connected to SDRV. The PCB trace connecting SDRV to the gate must be of minimal length and appropriate width to handle the h igh peak drive current and fast voltage transitions.

### 2.1.22 PDRV PIN

The g ate of th e I ow-side pri mary M OSFET i s connected to PD RV. The PC B tracing connecting PDRV to th e g ate must b e o f mi nimal le ngth an d appropriate width to han dle th e h igh-peak d rive currents and fast voltage transitions.

### 2.1.23 V<sub>DR</sub> PIN

The supply for the low-side drivers is connected to this pin and has an absolute maximum rating of +13.5V. This pin can be connected by an RC filter to the  $V_{DD}$  pin.

### 2.1.24 V<sub>DD</sub> PIN

The output of the internal +5.0V regulator is connected to this pin. It is recommended that a 1.0  $\mu$ F by pass capacitor be connected between this pin and the GND pin of the device. The by pass capacitor sh ould be physically placed close to the device.

### 2.1.25 V<sub>IN</sub> PIN

Input p ower connection pin of the device. I t is recommended that capacitance be placed between this pin and the GND pin of the device.

### 2.1.26 V<sub>S</sub> PIN

Analog input connected to the non-inverting input of the overvoltage com parator. T ypically us ed as output voltage overvoltage protection. The inverting input of the overvoltage comparator is controlled by the OV REF DAC.

### 2.1.27 I<sub>FB</sub> PIN

Error amplifier inverting feedback connection.

### 2.1.28 I<sub>COMP</sub> PIN

Error amplifier output signal.

### 2.1.29 EXPOSED PAD (EP)

It is recommended to connect the exposed p ad to  $A_{\mbox{\scriptsize GND}}.$

NOTES:

### 3.0 FUNCTIONAL DESCRIPTION

### 3.1 Linear Regulators

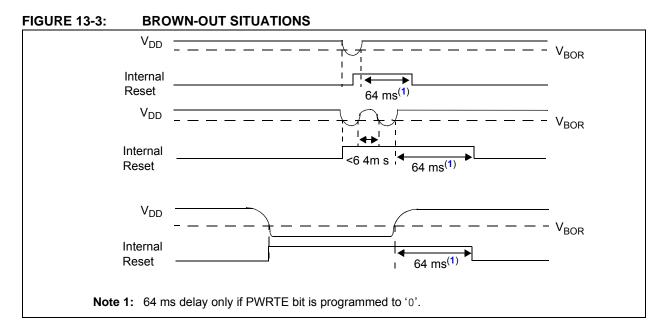

The operating input v oltage for the MCP19114/5 ranges from 4.5V to 42 V. There are two internal Low Dropout (LDO) voltage regulators. A 5V LDO is used to power the internal processor and provide a 5V output for ex ternal us age. A s econd LDO ( $V_{AVDD}$ ) is a 4V regulator and is used to p ower the remaining analog internal ci rcuitry. U sing a n L DO t o po wer th e MCP19114/5, the i nput voltage is monitored using a resistor di vider. The MCP19114/5 al so in corporate brown-out prot ection. R efer to Section 13.3 "Brown-out Reset (BOR)" for de tails. The PIC core will reset at 2.0V V<sub>DD</sub>.

### 3.2 Output Drive Circuitry

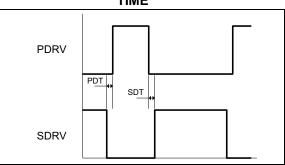

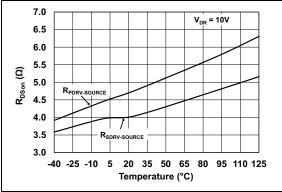

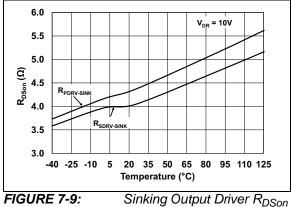

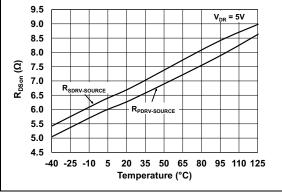

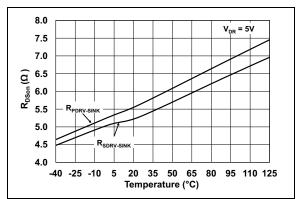

The MCP19114/5 integrate two low-side drivers used to d rive the e xternal I ow-side N -Channel power MOSFETs f or s ynchronous ap plications, s uch a s synchronous flyback and synchronous Cuk converters. Both con verter typ es can be co nfigured for non-synchronous control by replacing the synchronous FET with a diode. The fl yback is also capable of quasi-resonant operation. The MCP19114/5 can also be configured as a Boost or SEPIC switch-mode power supply (SM PS). In Boo st mode, non-synchronous fixed-frequency or non -synchronous gua si-resonant control can be utilized. This device can also be used as a SEPIC SMPS in fi xed-frequency non-synchronous mode. The low-side drive is capable of switching the MOSFET a th igh fre quency i nt ypical SM PS applications. The gate drive  $(V_{DR})$  can be supplied from 5V to 10V. The drive strength is capable of up to 1A sink/source with 10V gate dr ive an d d own t o 0.5A sink/source with 5V gate drive. A programmable delay is used to set the gate turn-on dead time. This prevents overlap and shoot-through currents that can decrease the converter efficiency. Each driver shall have its own EN input controlled by the microcontroller core.

### 3.3 Current Sense

The out put current is differentially se nsed by the MCP19114/5. In low -current applications, t his he lps maintain h igh system efficiency by minimizing power dissipation i n cu rrent se nse res istors. D ifferential current s ensing a lso minimizes external g round s hift errors. The internal differential amplifier has a precision gain of 10V/V.

### 3.4 Peak Current Mode

The M CP19114/5 is a peak current mode controlled device with the current sensing element in series with the prim ary si de M OSFET. Prog rammable Lea ding Edge Bl anking c an b e i mplemented to bl ank current spikes res ulting from tu rn on . The b lank tim e i s controlled from the ICLEBCON register.

Primary Input Current Offset Adjust is also available via user programmability, thus limiting peak primary input current. Th is of fset adj ustment i s c ontrolled b y th e ICOACON register.

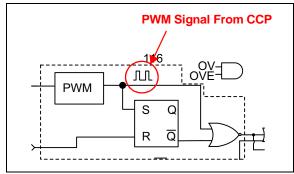

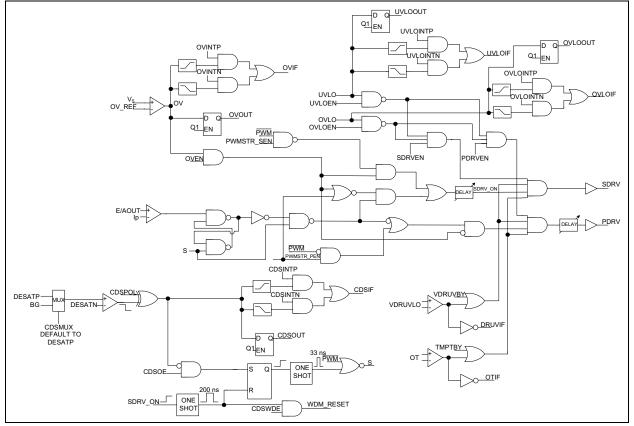

### 3.5 Magnetic Desaturation Detection

An internal comparator module is used to detect power train magnetic de saturation for q uasi-resonant applications. The comparator output is used as a signal to syn chronize the start of the next switching cycle. This ope ration d iffers from the trad itional fixed-frequency app lication. The D ESAT co mparator output can be en abled and routed in to the PWM circuitry or d isabled for fix ed-frequency applications. During Qu asi-Resonant (QR) o peration, the D ESAT comparator output is enabled and combined with a pair of one -shot ti mers a nd a flip-flop to s ustain PWM operation. Timer2 (TMR2) must be initialized and set to run a t a frequency lo wer th an the mi nimum Q R operating frequency. When the CDSWDE bit is set in the DESATCON register, TMR2 serves as a watchdog.

An example of the order of events for a Flyback SMPS in synchronous QR operation is as follows:

The primary gate drive (PDRV) goes high. The output of the DESAT comparator is high. The primary current increases until Ip reaches the level of the E rror Amp and causes PWM comparator output to go I ow. The PDRV goes low and the secondary gate drive (SDRV) goes high (after programmed dead time). This triggers the first one-shot to send a 200 ns pulse that resets the flip-flop and TM R2 (WDM RESET). The 20 0 ns one-shot pulse design is implemented to mask out any spurious transitions at the DESAT comparator output caused by switching noise. The SDRV stays high until the secondary winding completely runs out of energy, at which time the output capacitance begins to source current bac k th rough the winding an d sec ondary MOSFET. The DESAT comparator detects this and its output goes low. This sets the flip-flop and triggers the second one-shot to send a 33 ns pulse to the control logic, causing the SDRV to go low and the PDRV to go high (after programmed dead time). The cy cle the n repeats. If, for any reason, the reset one-shot does not fire, the WDM RESET signal stays low and TMR2 is allowed to run until the PWM signal kicks off a new cycle.

The desaturation comparator module is controlled by the DESATCON register.

### 3.6 Start-up

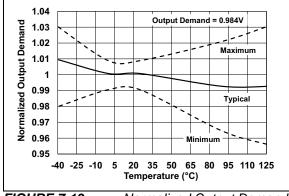

To c ontrol th e ou tput cur rent d uring s tart-up, th e MCP19114/5 h ave t he c apability t o mo notonically increase system current, at the user's discretion. This is a ccomplished through the c ontrol of the reference voltage DAC ( $V_{REF}$ ). The entire start-up profile is under user control via software.

### 3.7 Driver Control Circuitry

The internal driver control circuitry of the MCP19114/5 is comprised of an error amplifier (EA), a high-speed comparator and a latch similar to the MCP1631.

The error amplifier generates the control voltage used by the high-speed PWM comparator. There is a n internally gen erated reference v oltage, V REF. The difference or error be tween th is in ternal reference voltage and the actual feedback voltage is the control voltage. Som e a pplications w ill im plement p arked times where the ga te dr ives ar e not ac tive. For example, when ch anging be tween LED s trings an d after v oltage repo sitioning, the us er can dis able the gate drives and p ark the error am plifier o utput I ow. During the time when the EA is parked, its output will be clamped low (1 \* BG) such that it is in a known state when re activated. Be fore the out put s witches a re re-enabled, it may be necessary to re-enable the EA some time prior to en abling the output drivers. This prior-EA enable time will allow the EA to slew towards the intended target and prevent the secondary switch from tu rning on for an e xtensive peri od o f time, unintentionally discharging the output capacitance and tput vo Itage do wn. Ext ernal pulling the ou compensation is used to stabilize the control system.

Since the M CP19114/5 a re pea k cu rrent mode controlled, the comparator compares the primary peak current waveform (I<sub>P</sub>) that is based upon the current flowing in the primary side with the error amplifier control out put vo Itage. Thi s error am plifier control output vo Itage a Iso has us er-programmable s lope compensation su btracted from it. In fi xed-frequency applications, the slope compensation signal is generated to be greater than 1/2 the down slope of the inductor curr ent w aveform and is controlled by the SLPCRCON reg ister. Of fset ad just a bility is als o available to set the pe ak current limit of the primary switch for o vercurrent pr otection. The ran ge of the slope compensation ra mp i s specified. W hen th e current sense signal reaches the level of the control voltage minus slope compensation, the on c ycle is terminated and the external switch is latched off until the beginning of the next cycle which begins at the next clock cycle.

To improve current regulation at low levels, a pedestal voltage (VZC) set to the BG (1.23V) is implemented. This virtual ground serves as the reference for the error amplifier (A1), sl ope compensation, c urrent s ense amplifier (A2) and the  $I_P$  offset adjustment.

An S-R latch (Set-Rest-Flip-Flop) is used to prevent the PWM circuitry from turning the external switch on until the beginning of the next clock cycle.

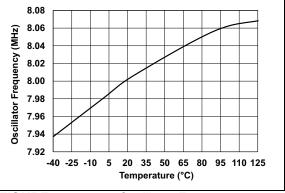

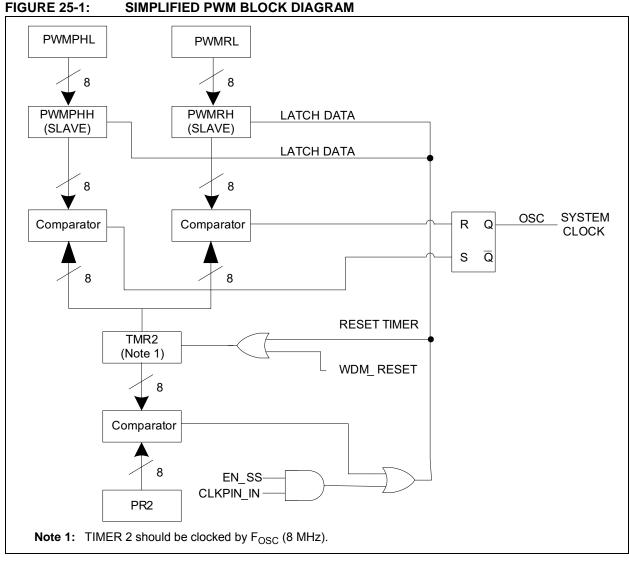

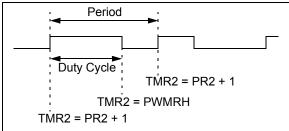

### 3.8 Fixed PWM Frequency

The switching frequency of the MCP19114/5 while not controlled b yt he D ESAT c omparator o utput i s generated by using a single edge of the 8 MHz internal clock. T he u ser set the MCP19114/5 switching frequency by configuring the PR 2 reg ister. The maximum allowable PDRV duty cycle is adjustable and is c ontrolled b yt he PW MRL register. The programmable range of the switching frequency will be 31.25 kHz to 2 MHz. The available switching frequency below 2 MHz is defined as  $F_{SW} = 8$  MHz/N, where N is a whole nu mber be tween  $4 \le N \le 256$ . R efer to Section 25.0 "Enhanced PWM Module" for details.

### 3.9 V<sub>REF</sub>

This reference is used to generate the v oltage connected to the n on-inverting input of the error amplifier. The entire analog control loop is raised to a virtual ground pedestal equal to the Band Gap voltage (1.23V).

### 3.10 OV REF

This reference is used to set the output overvoltage set point. It is compared to the  $V_S$  in put pin, which is typically proportional to the output voltage based on a resistor divider. OV protection, when enabled, can be set to a value for the protection of system circuitry or it can be used to "rip ple" regulate the converter output voltage for repositioning purposes. For details, refer to Register 6-4.

### 3.11 Independent Gate Drive with Programmable Delay

Two independent low-side gate drives are integrated for synchronous applications. Programmable delay has been implemented to improve efficiency and prevent shoot-through c urrents. Eac h gate drive has a n independent e nable in put c ontrolled by the PE1 register and programmable dead time controlled by the DEADCON register.

### 3.12 Temperature Management

### 3.12.1 THERMAL SHUTDOWN

To prot ect the MC P19114/5 from ov ertemperature conditions, a 150 °C jun ction tem perature the rmal shutdown has been implemented. When the junction temperature reaches this limit, the device disables the output drivers. I n Shu tdown mo de, bot h PD RV and SDRV outputs are disabled and the overtemperature flag (OTIF) is s et in the PI R2 re gister. When the junction temperature is reduced by 20°C to 130°C, the MCP19114/5 c an re sume n ormal ou tput dr ive switching.

### 3.12.2 TEMPERATURE REPORTING

The MCP19114/5 have a second on-chip temperature monitoring circuit that can be read by the ADC through the analog test MUX. Refer to **Section 20.0 "Internal Temperature In dicator M odule"** for d etails on this internal temperature monitoring circuit.

#### **ELECTRICAL CHARACTERISTICS** 4.0

#### 4.1 **ABSOLUTE MAXIMUM RATINGS †**

| V <sub>IN</sub> -V <sub>GND</sub> (operating)<br>V <sub>IN</sub> (transient < 500 ms) | -0.3V to +44V                                          |

|---------------------------------------------------------------------------------------|--------------------------------------------------------|

| V <sub>IN</sub> (transient < 500 ms)                                                  | +48V                                                   |

| PDRV                                                                                  | (GND - 0.3V) to (V <sub>DR</sub> +0 .3V)               |

| SDRV                                                                                  |                                                        |

| V <sub>DD</sub> Internally Generated                                                  |                                                        |

| V <sub>DR</sub> Externally Generated                                                  | +13.5V                                                 |

| Voltage on MCLR with respect to GND                                                   | -0.3V to +13.5V                                        |

| Maximum voltage: any other pin                                                        | +(V <sub>GND</sub> - 0.3V) to (V <sub>DD</sub> + 0.3V) |

| Maximum output current sunk by any single I/O pin                                     | 25 mA                                                  |

| Maximum output current sourced by any single I/O pin                                  | 25 mA                                                  |

| Maximum current sunk by all GPIO                                                      | 90 mA                                                  |

| Maximum current sourced by all GPIO                                                   | 35 mA                                                  |

| Storage Temperature                                                                   | 65°C to +150°C                                         |

| Maximum Junction Temperature                                                          | +150°C                                                 |

| Operating Junction Temperature                                                        |                                                        |

| ESD protection on all pins (HBM)                                                      |                                                        |

| ESD protection on all pins (MM)                                                       | 200V                                                   |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 4.2 **Electrical Characteristics**

| Parameters                                      | Sym.                                                                | Min.  | Тур.  | Max.  | Units | Conditions                                           |

|-------------------------------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|------------------------------------------------------|

| Input                                           |                                                                     |       |       |       |       |                                                      |

| Input Voltage                                   | V <sub>IN</sub>                                                     | 4.5   |       | 42    | V     |                                                      |

| Input Quiescent<br>Current                      | ۱ <sub>Q</sub>                                                      | —5    |       | 10    | mA    | Not Switching, +V <sub>SEN</sub> =5 V                |

| Shutdown Current                                | I <sub>SHDN</sub>                                                   | —3    | 0     | 150   | μA    | V <sub>IN</sub> = 12V<br>Note 1                      |

| Linear Regulator V <sub>D</sub>                 | D                                                                   |       |       |       |       |                                                      |

| Internal Circuitry<br>Bias Voltage              | V <sub>DD</sub>                                                     | 4.75  | 5.0   | 5.5   | VV    | <sub>IN</sub> = 6.0V to 42V                          |

| Maximum External V <sub>DD</sub> Output Current | I <sub>DD_OUT</sub>                                                 | 35    |       |       | mA    | V <sub>IN</sub> = 6.0V to 42V,<br>Note 3             |

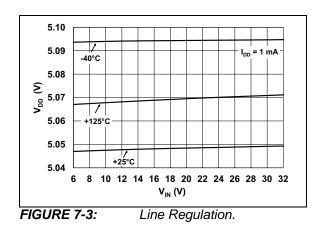

| Line Regulation                                 | ΔV <sub>DD-OUT</sub> /<br>(V <sub>DD-OUT</sub> * ΔV <sub>IN</sub> ) | -0.1  | 0.002 | 0.1   | %/V   | $(V_{DD} + 1 .0V) \le V_{IN} \le 20V$<br>Note 3      |

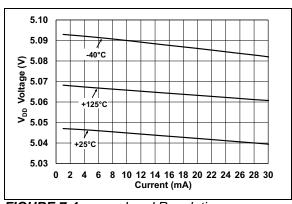

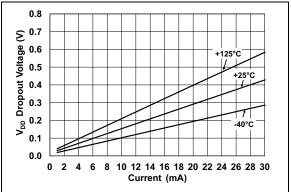

| Load Regulation                                 | ΔV <sub>DD-OUT</sub> /<br>V <sub>DD-OUT</sub>                       | -0.65 | 0.1   | +0.65 | %I    | DD_OUT = 1 mA to 20 mA<br>Note 3                     |

| Output Short Circuit<br>Current                 | I <sub>DD_SC</sub>                                                  | —5    | 0     |       | mA    | V <sub>IN</sub> =( V <sub>DD</sub> +1 .0V)<br>Note 3 |

- 2: Ensured by design, not production tested.

- **3:** V<sub>DD</sub> is the voltage present at the V<sub>DD</sub> pin.

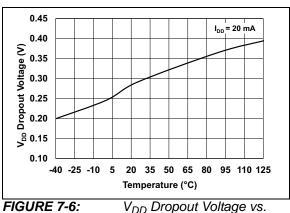

- 4: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between  $V_{IN}$  and  $V_{DD}$ .

- 5: The V<sub>DD</sub> LDO will limit the total source current to a maximum of 35 mA. Individually each pin can source a maximum of 15 mA.

| Parameters                          | Sym.                              | Min. | Тур. | Max. | Units | Conditions                                                                                                                                                      |

|-------------------------------------|-----------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dropout Voltage                     | V <sub>IN</sub> - V <sub>DD</sub> | _    | 0.3  | 0.5  | V     | I <sub>DD_OUT</sub> = 20 mA,<br>Note 3, Note 4                                                                                                                  |

| Power Supply<br>Rejection Ratio     | PSRR <sub>LDO</sub>               |      | 60   |      | dB    | $\label{eq:states} \begin{array}{l} f \leq 1000 \text{ Hz}, \\ I_{DD\_OUT} = 25 \text{ mA} \\ C_{IN} = 0 \ \mu\text{F}, \ C_{DD} = 1 \ \mu\text{F} \end{array}$ |

| Linear Regulator V <sub>AV</sub>    | /DD                               |      |      |      |       |                                                                                                                                                                 |

| Internal Analog<br>Supply Voltage   | V <sub>AVDD</sub>                 | —4   | .0   | —    | V     |                                                                                                                                                                 |

| Band Gap Voltage                    | BG                                |      | 1.23 |      | V     | Trimmed at 1.0% tolerance                                                                                                                                       |

| Band Gap<br>Tderance                | BG <sub>TOL</sub>                 | -2.5 | —    | +2.5 | %     |                                                                                                                                                                 |

| Input UVLO Voltage                  |                                   |      |      |      |       |                                                                                                                                                                 |

| UVLO Range                          | UVLO <sub>ON</sub>                | 4.0  | _    | 20   | VV    | <sub>IN</sub> Falling                                                                                                                                           |

| UVLO <sub>ON</sub> Trip<br>Tderance | UVLO <sub>TOL</sub>               | -14  | -    | 14   | %V    | <sub>IN</sub> Falling<br>UVLO trip set to 9V<br>VINUVLO = 0x21h                                                                                                 |

| UVLO Hysteresis                     | UVLO <sub>HYS</sub>               |      | 4    | _    | %     | Hysteresis is based upon<br>the UVLO <sub>ON</sub> setting<br>UVLO trip set to 9V<br>VINUVLO = 0x21h                                                            |

| Resolution                          | nbits                             | _    | 6    | _    | Bits  | Logarithmic Steps                                                                                                                                               |

| UVLO Comparator                     |                                   |      |      |      |       |                                                                                                                                                                 |

| Input-to-Output<br>Delay            | TD                                | —    | 5    | _    | μs    | 100 ns rise time to 1V<br>overdrive on V <sub>IN</sub><br>V <sub>IN</sub> > UVLO to flag set                                                                    |

| Input OVLO Voltage                  |                                   |      |      |      |       |                                                                                                                                                                 |

| OVLO Range                          | OVLO <sub>ON</sub>                | 8.8  | _    | 44   | VV    | IN Rising                                                                                                                                                       |

| OVLO <sub>ON</sub> Trip<br>Tderance | OVLO <sub>TOL</sub>               | -14  | _    | 14   | %V    | <sub>IN</sub> Rising<br>OVLO trip set to 18V<br>VINOVLO = 0x1Fh                                                                                                 |

| OVLO Hysteresis                     | OVLO <sub>HYS</sub>               | —    | 5    |      | %     | Hysteresis is based upon the<br>OVLO <sub>ON</sub> setting<br>OVLO trip set to 18V<br>VINOVLO = 0x1Fh                                                           |

| Resolution                          | nbits                             | _    | 6    |      | Bits  | Logarithmic Steps                                                                                                                                               |

| OVLO Comparator                     |                                   |      |      |      |       |                                                                                                                                                                 |

| Input-to-Output<br>Delay            | TD                                | _    | 5    | _    | μs    | 100 ns rise time to 1V<br>overdrive on V <sub>IN</sub><br>V <sub>IN</sub> > OVLO to flag set                                                                    |

Note 1: Refer to Section 15.0 "Power-Down Mode (Sleep)".

- **2:** Ensured by design, not production tested.

- **3:**  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

**4:** Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between V<sub>IN</sub> and V<sub>DD</sub>.

The V<sub>DD</sub> LDO will limit the total source current to a maximum of 35 mA. Individually each pin can source a maximum of 15 mA.

| Parameters                         | Sym.                    | Min. | Тур. | Max.   | Units | Conditions                                                                                  |

|------------------------------------|-------------------------|------|------|--------|-------|---------------------------------------------------------------------------------------------|

| Output OV DAC                      |                         |      |      | •      | •     |                                                                                             |

| Resolution                         | nbits                   | _    | 8    |        | Bits  | Linear DAC                                                                                  |

| Full Scale Range                   | FSR                     | 0    | _    | 2 * BG | V     |                                                                                             |

| Tolerance                          | OVREF <sub>TOL</sub>    | -10  | _    | +10    | %     | Full Scale, Code = 0xFF                                                                     |

| Output OV Compara                  | tor                     | L    | 4    |        | 1     |                                                                                             |

| OV Hysteresis                      | OV <sub>HYS</sub>       | —5   | 0    |        | mV    |                                                                                             |

| Input Bias Current                 | I <sub>BIAS</sub>       | —±   | 1    |        | μA    |                                                                                             |

| Common-Mode<br>Input Voltage Range | V <sub>CMR</sub>        | 0—   |      | 3.0    | V     | Note 2                                                                                      |

| Input-to-Output<br>Delay           | TD                      | _    | 200  | —      | ns    | Note 2<br>100 ns rise time to 1V<br>overdrive on $V_S$<br>$V_S > OV$ to flag set            |

| Voltage Reference D                | AC (V <sub>REF</sub> )  |      |      |        |       |                                                                                             |

| Resolution                         | nbits                   |      | 8    |        | V/V   | Linear DAC                                                                                  |

| Full Scale Range                   | FSR                     | BG   | _    | 2 * BG | V     | Pedestal set to BG                                                                          |

| Voltage Reference D                | AC (V <sub>REF2</sub> ) |      |      |        |       |                                                                                             |

| Resolution                         | nbits                   |      | 8    |        | Bits  | Linear DAC                                                                                  |

| Full Scale Range                   | FSR                     | 0    | _    | BG     | V     |                                                                                             |

| Sink Current                       | I <sub>SINK</sub>       | -3   |      |        | mA    | $V_{REF2} = 0 V$ ,<br>R <sub>L</sub> = 3 00 $\Omega$ to BG                                  |

| Source Current                     | ISOURCE                 | 3    |      |        | mA    | $V_{REF2}$ =B G,<br>R <sub>L</sub> =3 00 $\Omega$ to GND                                    |

| Tderance                           | VREF2 <sub>TOL</sub>    | -10  | —    | +10    | %     | Full Scale, Code = 0xFF                                                                     |

| Current Sense Ampl                 | ifier (A2)              |      |      |        |       |                                                                                             |

| Amplifier PSRR                     | PSRR                    | —    | 65   | _      | dB    | V <sub>CM</sub> =2 * BG                                                                     |

| Closed Loop<br>Voltage Gain        | A2 <sub>VCL</sub>       | —1   | 0    | _      | V/V   | $R_L$ =5 kΩ to 2.048V,<br>100 mV < A2 <<br>V <sub>AVDD</sub> – 100 mV, V <sub>CM</sub> =B G |

| Low-Level Output                   | V <sub>OL</sub>         | —5   | 00   | _      | mV    | $R_L = 5 k\Omega$ to 2.048V                                                                 |

| Gain Bandwidth<br>Product          | GBWP                    | _    | 10   | —      | MHz   | V <sub>AVDD</sub> =4 V                                                                      |

| Input Impedance                    | R <sub>IN</sub>         | —1   | 0    | —      | kΩ    |                                                                                             |

| Sink Current                       | I <sub>SINK</sub>       | -3   |      |        | mA    | I <sub>SP</sub> =I <sub>SN</sub> =G ND<br>R <sub>L</sub> =3 00Ω to 2 * BG                   |

| Source Current                     | ISOURCE                 | 3    |      |        | mA    | $I_{SP} = I_{SN} = G ND$<br>R <sub>L</sub> = 3 00 $\Omega$ to GND                           |

- 2: Ensured by design, not production tested.

- **3:**  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

- **4:** Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between V<sub>IN</sub> and V<sub>DD</sub>.

- **5:** The V<sub>DD</sub> LDO will limit the total source current to a maximum of 35 mA. Individually each pin can source a maximum of 15 mA.

| Electrical Specificat<br>apply over the T <sub>A</sub> range | ions: Unless other<br>ge of -40°C to +12 | rwise noted, V <sub>I</sub><br>5°C | <sub>N</sub> = 12V, F <sub>S</sub> | <sub>W</sub> =1 50 kH: | z, T <sub>A</sub> =+ 2 | 25°C, <b>Boldface</b> specifications                                                    |

|--------------------------------------------------------------|------------------------------------------|------------------------------------|------------------------------------|------------------------|------------------------|-----------------------------------------------------------------------------------------|

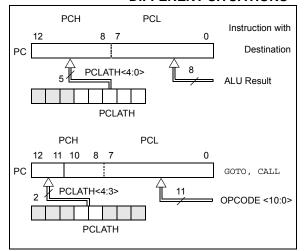

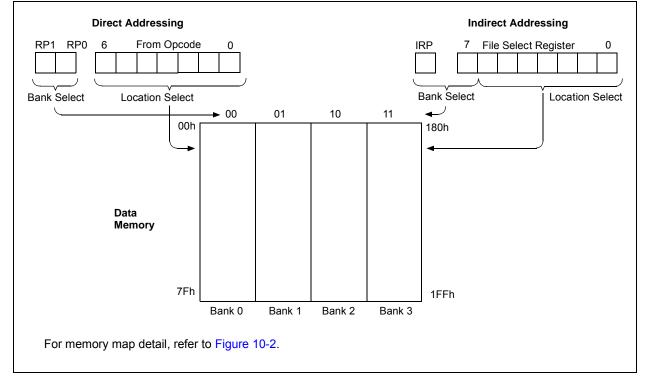

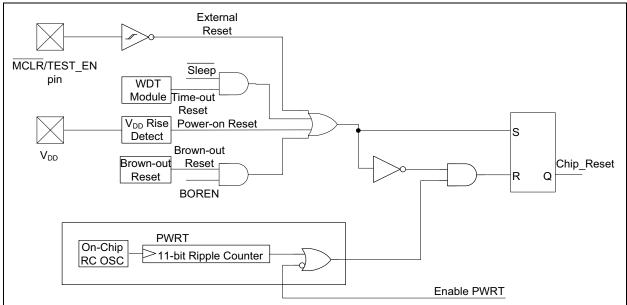

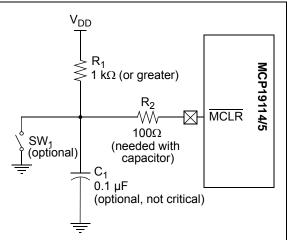

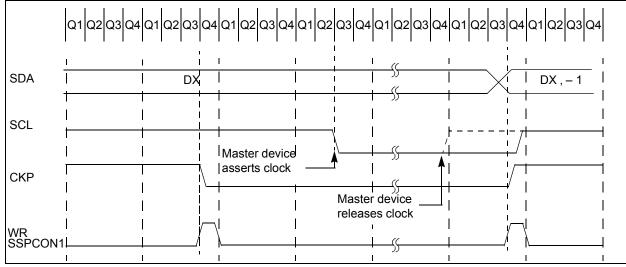

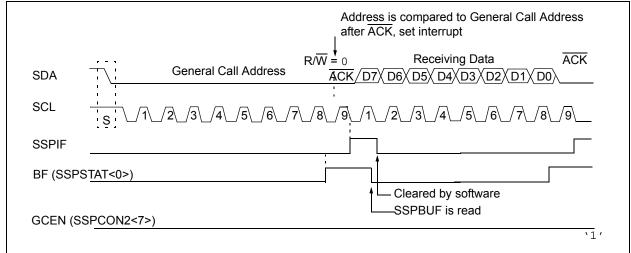

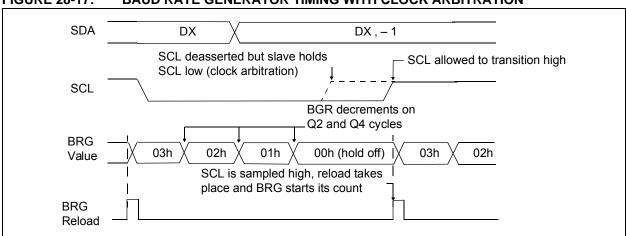

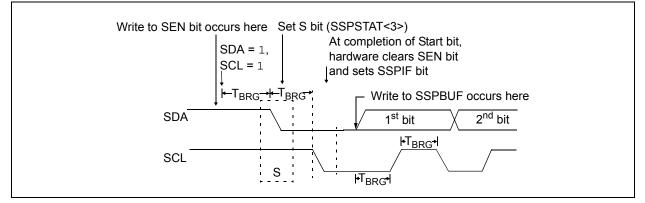

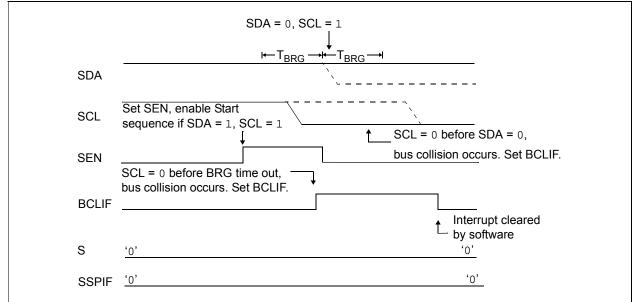

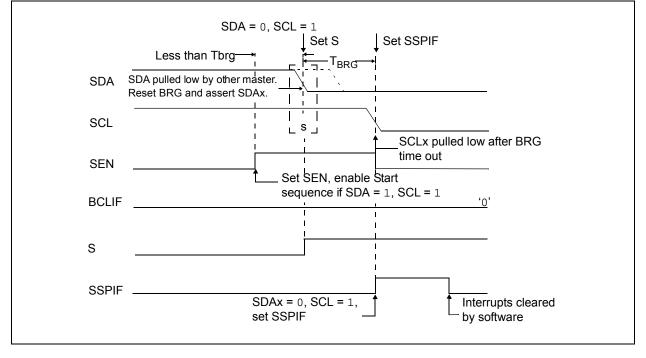

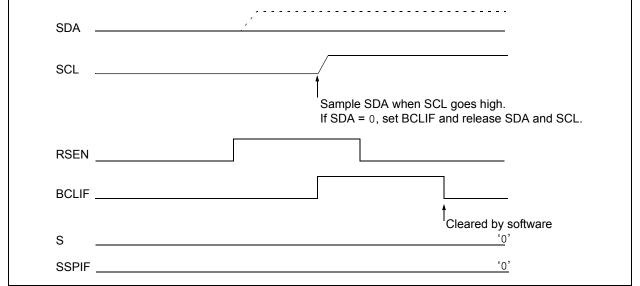

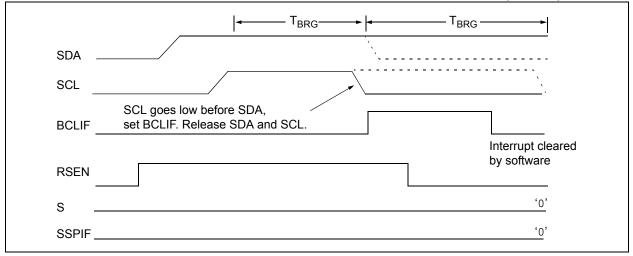

| Parameters                                                   | Sym.                                     | Min.                               | Тур.                               | Max.                   | Units                  | Conditions                                                                              |